Intel Core i7/ Celeron COM Express Module

## **User's Manual**

1st Ed - 6 April 2011

#### **FCC Statement**

THIS DEVICE COMPLIES WITH PART 15 FCC RULES. OPERATION IS SUBJECT TO THE FOLLOWING TWO CONDITIONS:

(1) THIS DEVICE MAY NOT CAUSE HARMFUL INTERFERENCE.

(2) THIS DEVICE MUST ACCEPT ANY INTERFERENCE RECEIVED INCLUDING INTERFERENCE THAT MAY CAUSE UNDESIRED OPERATION.

THIS EQUIPMENT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS "A" DIGITAL DEVICE, PURSUANT TO PART 15 OF THE FCC RULES.

THESE LIMITS ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST HARMFUL INTERFERENCE WHEN THE EQUIPMENT IS OPERATED IN A COMMERCIAL ENVIRONMENT. THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND, IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTION MANUAL, MAY CAUSE HARMFUL INTERFERENCE TO RADIO COMMUNICATIONS.

OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE HARMFUL INTERFERENCE IN WHICH CASE THE USER WILL BE REQUIRED TO CORRECT THE INTERFERENCE AT HIS OWN EXPENSE.

## **Copyright Notice**

Copyright © 2011 Avalue Technology Inc., ALL RIGHTS RESERVED.

No part of this document may be reproduced, copied, translated, or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the prior written permission of the original manufacturer.

## **Trademark Acknowledgement**

Brand and product names are trademarks or registered trademarks of their respective owners.

## **Life Support Policy**

Avalue Technology's PRODUCTS ARE NOT FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE PRIOR WRITTEN APPROVAL OF Avalue Technology Inc.

As used here in:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into body, or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## A Message to the Customer

#### **Avalue Customer Services**

Each and every Avalue's product is built to the most exacting specifications to ensure reliable performance in the harsh and demanding conditions typical of industrial environments. Whether your new Avalue device is destined for the laboratory or the factory floor, you can be assured that your product will provide the reliability and ease of operation for which the name Avalue has come to be known.

Your satisfaction is our primary concern. Here is a guide to Avalue's customer services. To ensure you get the full benefit of our services, please follow the instructions below carefully.

## **Technical Support**

We want you to get the maximum performance from your products. So if you run into technical difficulties, we are here to help. For the most frequently asked questions, you can easily find answers in your product documentation. These answers are normally a lot more detailed than the ones we can give over the phone. So please consult the user's manual first.

To receive the latest version of the user's manual; please visit our Web site at: <a href="http://www.avalue.com.tw/">http://www.avalue.com.tw/</a>

If you still cannot find the answer, gather all the information or questions that apply to your problem, and with the product close at hand, call your dealer. Our dealers are well trained and ready to give you the support you need to get the most from your Avalue's products. In fact, most problems reported are minor and are able to be easily solved over the phone. In addition, free technical support is available from Avalue's engineers every business day. We are always ready to give advice on application requirements or specific information on the installation and operation of any of our products. Please do not hesitate to call or e-mail us.

#### **Headquarters and Branch**

#### Avalue Technology Inc.

7F, 228, Lian-cheng Road, Chung Ho City, Taipei,

Taiwan

Tel:+886-2-8226-2345 Fax: +886-2-8226-2777

Information: sales@avalue.com.tw

Service: service@avalue.com.tw

#### **Avalue USA**

#### **Avalue Technology Inc.**

9 Timber Lane, Marlboro, NJ 07746-1443

Tel: (732) 414-6500 Fax: (732) 414-6501

Information: <a href="mailto:sales@avalue-usa.com">sales@avalue-usa.com</a>

Service: <a href="mailto:support@avalue-usa.com">support@avalue-usa.com</a>

#### **BCM Advanced Research**

## BCM Advanced Research an Avalue Company

7 Marconi, Irvine, CA92618

Tel: +1-949-470-1888 Fax: +1-949-470-0971

Information: BCMSales@bcmcom.com

Web: www.bcmcom.com

#### **Avalue Europe**

#### **Avalue Europe A/S**

Moelledalen 22C, 3140 Aalsgaarde, Denmark Tel: +45-7025-0310

Fax:+45-4975-5026

Information: <a href="mailto:sales.europe@avalue.com.tw">sales.europe@avalue.com.tw</a>

Service: <a href="mailto:service.europe@avalue.com.tw">service.europe@avalue.com.tw</a>

#### **Avalue China**

#### Avalue Technology Inc.

Room 805, Building 9, No. 99 Tianzhou Rd.,

Caohejing Development Area,

Xuhui District, Shanghai Tel: +86-21-5169-3609 Fax:+86-21-5445-3266

Information: <a href="mailto:sales.china@avalue.com.cn">sales.china@avalue.com.cn</a>

Service: service@avalue.com.tw

#### **Avalue Japan**

#### Avalue Technology Inc.

2F keduka-Bldg, 2-27-3 Taito,

Taito-Ku, Tokyo 110-0016 Japan

Tel: +81-3-5807-2321

Fax: +81-3-5807-2322

Information: <a href="mailto:sales.japan@avalue.com.tw">sales.japan@avalue.com.tw</a>

Service: <a href="mailto:service@avalue.com.tw">service@avalue.com.tw</a>

## **Product Warranty**

Avalue warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Avalue, or which have been subject to misuse, abuse, accident or improper installation. Avalue assumes no liability under the terms of this warranty as a consequence of such events. Because of Avalue's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If any of Avalue's products is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time, and freight. Please consult your dealer for more details. If you think you have a defective product, follow these steps:

- Collect all the information about the problem encountered. (For example, CPU type and speed, Avalue's products model name, hardware & BIOS revision number, other hardware and software used, etc.) Note anything abnormal and list any on-screen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information available.

- 3. If your product is diagnosed as defective, obtain an RMA (return material authorization) number from your dealer. This allows us to process your good return more quickly.

- 4. Carefully pack the defective product, a complete Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

# **Contents**

| 1. Gettir | ng Started                                          | 9  |

|-----------|-----------------------------------------------------|----|

| 1.1 Safe  | ety Precautions                                     | 9  |

| 1.2 Pac   | king List                                           | 9  |

| 1.3 Doc   | cument Amendment History                            | 10 |

| 1.4 Mar   | nual Objectives                                     | 11 |

| 1.5 Sys   | tem Specifications                                  | 12 |

| 1.6 Arcl  | nitecture Overview – Block Diagram                  | 14 |

| 2. Hardy  | vare Configuration                                  | 15 |

| 2.1 Pro   | duct Overview                                       | 16 |

| 2.2 Inst  | allation Procedure                                  | 17 |

| 2.2.1 M   | ain Memory                                          | 18 |

|           | nector List                                         |    |

| 2.4 Set   | ting Jumpers & Connectors                           | 21 |

| 2.4.1 A   | T/ATX mode selector (SW1)                           | 21 |

| 2.4.1.1   | Signal Description –AT/ATX mode selection           |    |

| 2.4.2 C   | OM Express Connector 1 (CN2A)                       | 22 |

| 2.4.2     | Signal Description – COM Express Connector 1 (CN2A) | 26 |

| 2.4.2     | .1 Audio Signals                                    | 26 |

| 2.4.2     | .2 Gigabit Ethernet Signals                         | 26 |

| 2.4.2     |                                                     |    |

| 2.4.2     | .4 Flat Panel LVDS Signals                          | 27 |

| 2.4.2     |                                                     |    |

| 2.4.2     |                                                     |    |

| 2.4.2     |                                                     |    |

| 2.4.2     | .8 Power Signals                                    | 28 |

| 2.4.2     | .9 Power & System Management Signals                | 28 |

| 2.4.2     | .10 SATA Signals                                    | 29 |

| 2.4.2     | .11 VGA Signals                                     | 29 |

| 2.4.2     | .12 USB Signals                                     | 29 |

|           | OM Express Connector 2 (CN2B)                       |    |

| ·         | gnal Description – COM Express Connector 2 (CN2B)   |    |

|           | .1 IDE Signals                                      |    |

| 2.4.3     | ő                                                   |    |

| 2.4.3     | .3 PCI Signals                                      | 35 |

| 2.4.3     | .4 PCI Express Graphics Signals                     | 35 |

|               | <b>U</b> 3                            | Ci 3 Mailua |

|---------------|---------------------------------------|-------------|

| 3. BIOS Setup |                                       | 36          |

| 3.1 Introduc  | tion                                  | 37          |

| 3.2 Starting  | Setup                                 | 37          |

| 3.3 Using Se  | etup                                  | 38          |

| 3.4 Getting I | Help                                  | 39          |

| 3.5 In Case   | of Problems                           | 39          |

| 3.6 BIOS se   | etup                                  | 40          |

| 3.6.1 Main M  | lenu                                  | 40          |

| 3.6.1.1 Sy    | ystem Language                        | 40          |

| 3.6.1.2 Sy    | ystem Date                            | 40          |

| 3.6.1.3 Sy    | ystem Time                            | 40          |

| 3.6.2 Advanc  | ced Menu                              | 41          |

| 3.6.2.1 PC    | CI Subsystem Settings                 | 42          |

| 3.6.2.2 A     | CPI Settings                          | 44          |

| 3.6.2.3 Tı    | rusted computing                      | 45          |

| 3.6.2.4 S5    | 5 RTC Wake Settings                   | 46          |

| 3.6.2.5 Cl    | PU Configuration                      | 47          |

| 3.6.2.6 SA    | ATA Configuration                     | 49          |

| 3.6.2.7 In    | ntel IGD SWSCI OpRegion configuration | 50          |

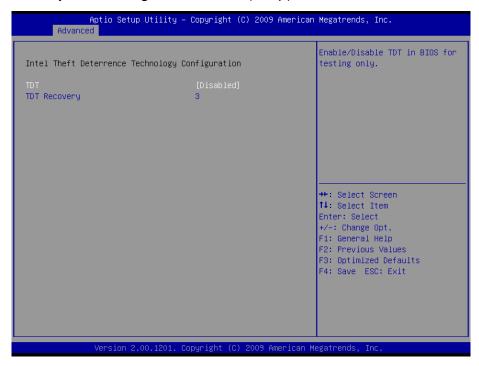

| 3.6.2.8 In    | ntel TDT (AT-p) Configuration         | 52          |

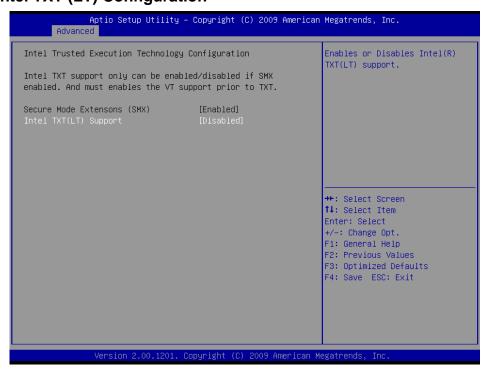

| 3.6.2.9 In    | ntel TXT (LT) Configuration           | 53          |

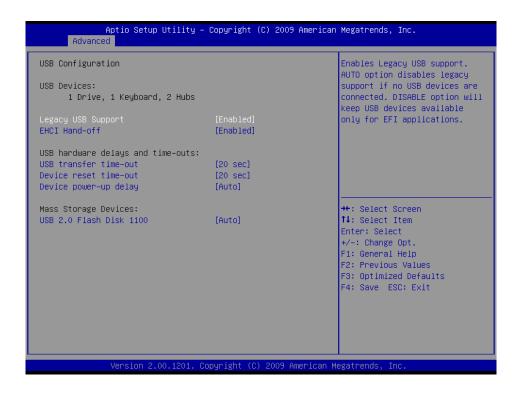

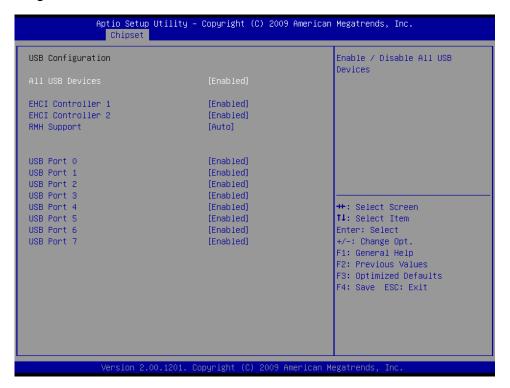

| 3.6.2.10 U    | SB Configuration                      | 54          |

| 3.6.2.10.1    | Legacy USB support                    | 54          |

| 3.6.2.10.2    | ECHI hand-off                         | 54          |

| 3.6.2.10.3    | USB transfer timeout                  | 54          |

| 3.6.2.10.4    | Device Reset timeout                  | 55          |

| 3.6.2.10.5    | Device Power-up delay                 | 55          |

| 3.6.2.10.6    | Mass Storage Devices                  | 55          |

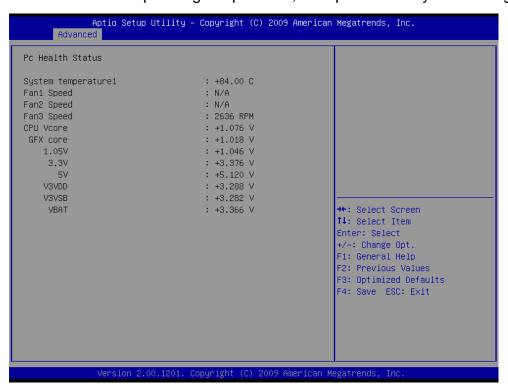

| 3.6.2.11 H    | /W Monitor                            | 55          |

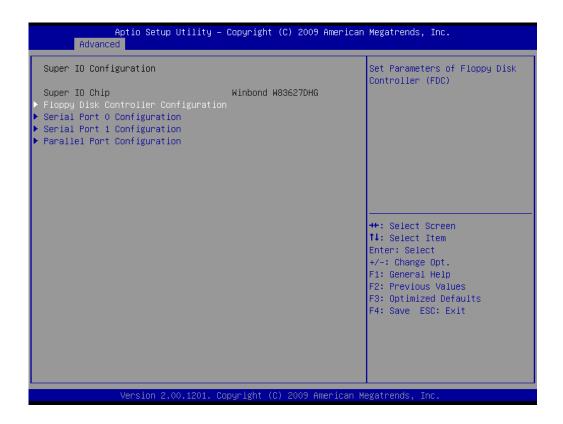

| 3.6.2.12 Su   | uper IO Configuration                 | 57          |

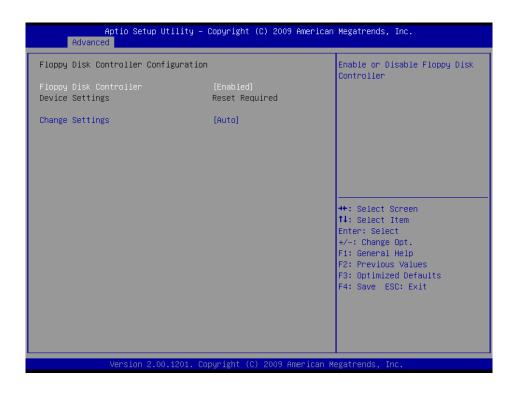

| 3.6.2.12.1    | Floppy Disk Controller Configuration  | 58          |

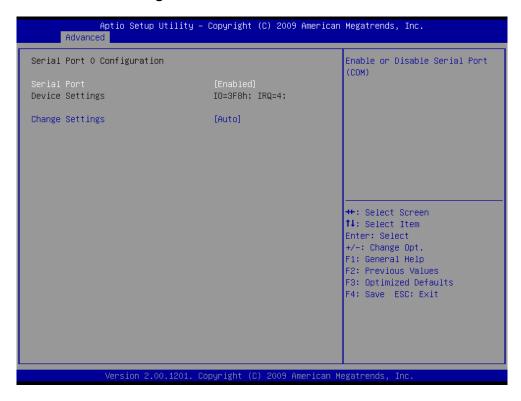

| 3.6.2.12.2    | Serial Port 0 Configuration           | 59          |

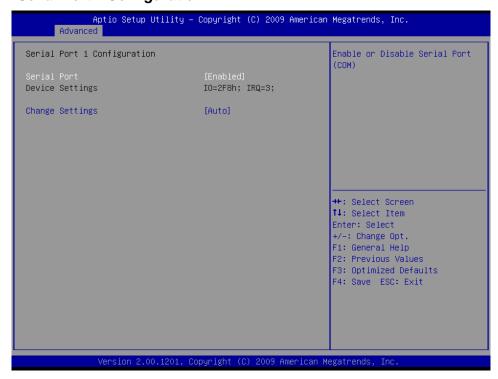

| 3.6.2.12.3    | Serial Port 1 Configuration           | 60          |

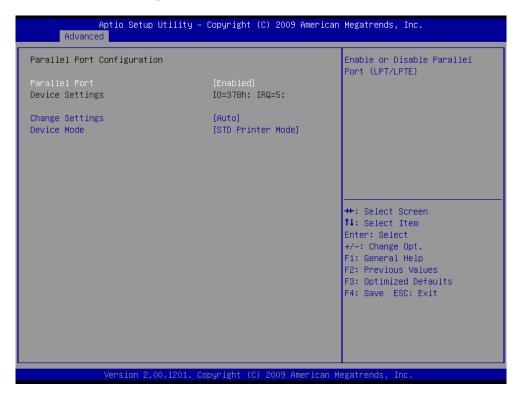

| 3.6.2.12.4    | Parallel Port Configuration           | 61          |

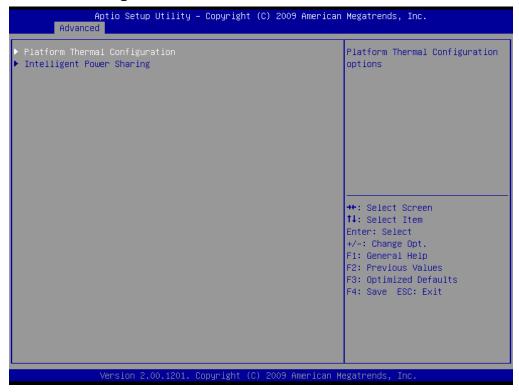

| 3.6.2.13 Th   | hermal Configuration                  | 62          |

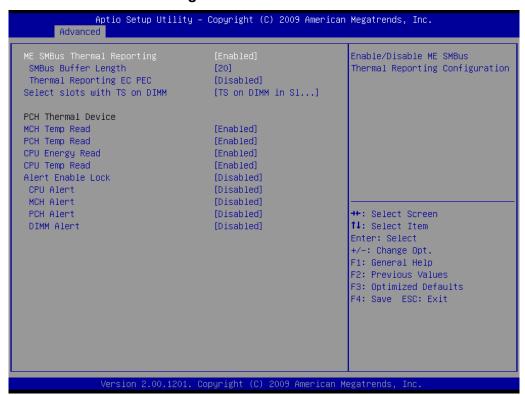

| 3.6.2.13.1    | Platform thermal Configuration        | 62          |

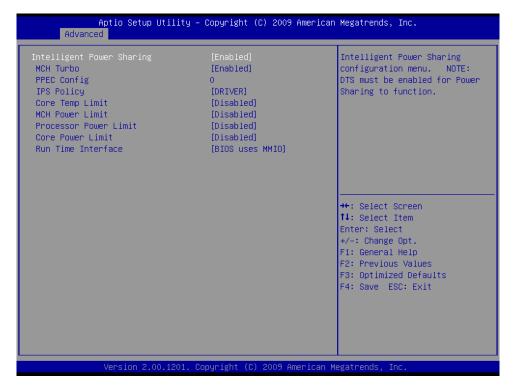

| 3.6.2.13.2    | Intelligent Power Sharing             | 64          |

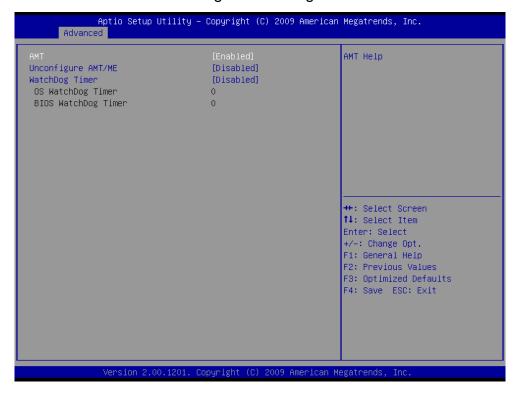

| 3.6.2.14 A    | MT Configuration                      | 65          |

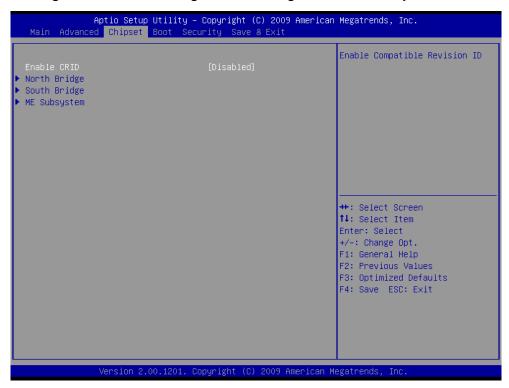

| 3.6.3 Advanc  | ced Chipset Features                  | 66          |

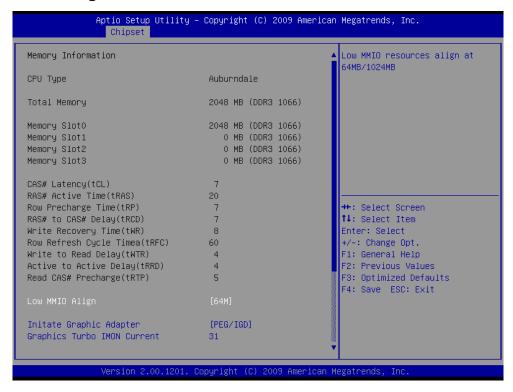

| 2621 N        | outh Duidge                           | 67          |

| 3.6.3.1.1 CAS # Latency (tCL)                          |    |

|--------------------------------------------------------|----|

| 3.6.3.1.2 RAS # Active Time (tRAS)                     |    |

| 3.6.3.1.3 Row Precharge Time (tRP)                     |    |

| 3.6.3.1.4 RAS# to CAS# Delay (tRCD)                    |    |

| 3.6.3.1.5 Write Recovery Time (tWR)                    | 68 |

| 3.6.3.1.6 Row Refresh Cycle (tRFC)                     | 68 |

| 3.6.3.1.7 Write to Read Delay (tWTR)                   | 68 |

| 3.6.3.1.8 Active to Active (tRRD)                      | 68 |

| 3.6.3.1.9 Read CAS# Precharge (tRTP)                   | 68 |

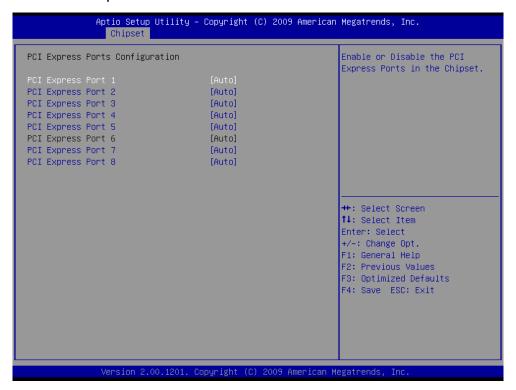

| 3.6.3.2 South Bridge                                   | 69 |

| 3.6.3.2.1 PCI Express Ports Configuration              | 70 |

| 3.6.3.2.2 USB Configuration                            | 71 |

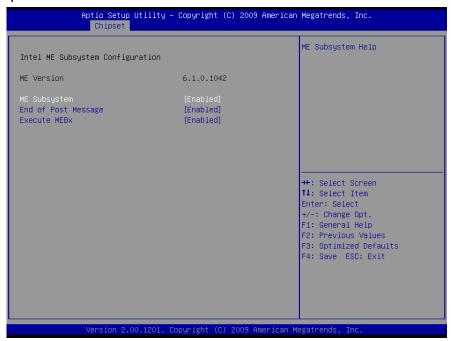

| 3.6.3.3 ME Subsystem                                   | 72 |

| 3.6.4 Boot                                             | 73 |

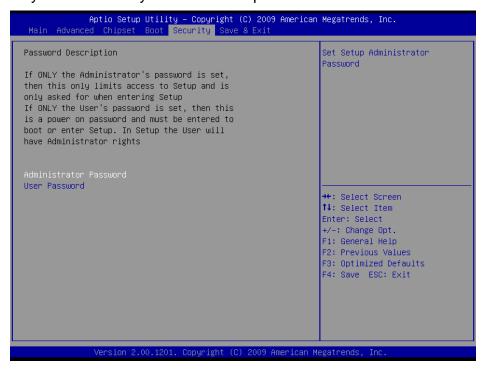

| 3.6.5 Security                                         | 74 |

| 3.6.5.1 Administrator Password                         | 74 |

| 3.6.5.2 User Password                                  | 74 |

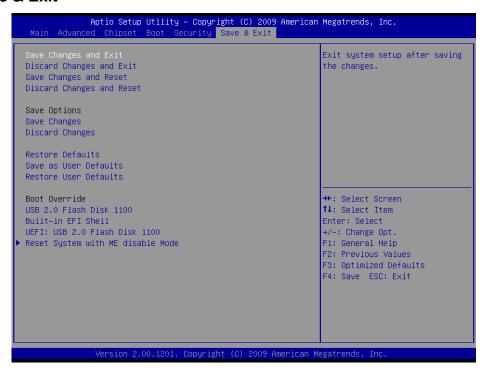

| 3.6.6 Save & Exit                                      | 75 |

| 3.6.6.1 Save Changes and Exit                          | 75 |

| 3.6.6.2 Discard Changes and Exit                       | 75 |

| 3.6.6.3 Save Changes and Reset                         | 75 |

| 3.6.6.4 Discard Changes and Reset                      | 75 |

| 3.6.6.5 Save Changes                                   | 75 |

| 3.6.6.6 Discard Changes                                | 76 |

| 3.6.6.7 Restore Defaults                               | 76 |

| 3.6.6.8 Save as user defaults                          | 76 |

| 3.6.6.9 Restore as user defaults                       | 76 |

| 3.6.6.10 Boot override                                 | 76 |

| 3.6.6.11 Reset system with ME disable mode             | 76 |

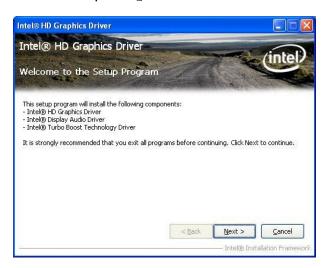

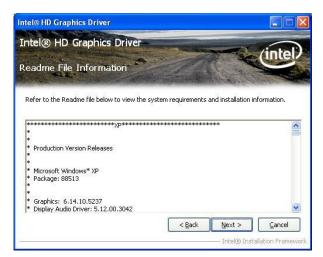

| Drivers Installation                                   | 77 |

| .1 Install Chipset Driver (For Intel QM57)             | 78 |

| .2 Install Display Driver (For Intel QM57)             |    |

| .3 Install Ethernet Driver (For Intel 82574L/ 82577LM) |    |

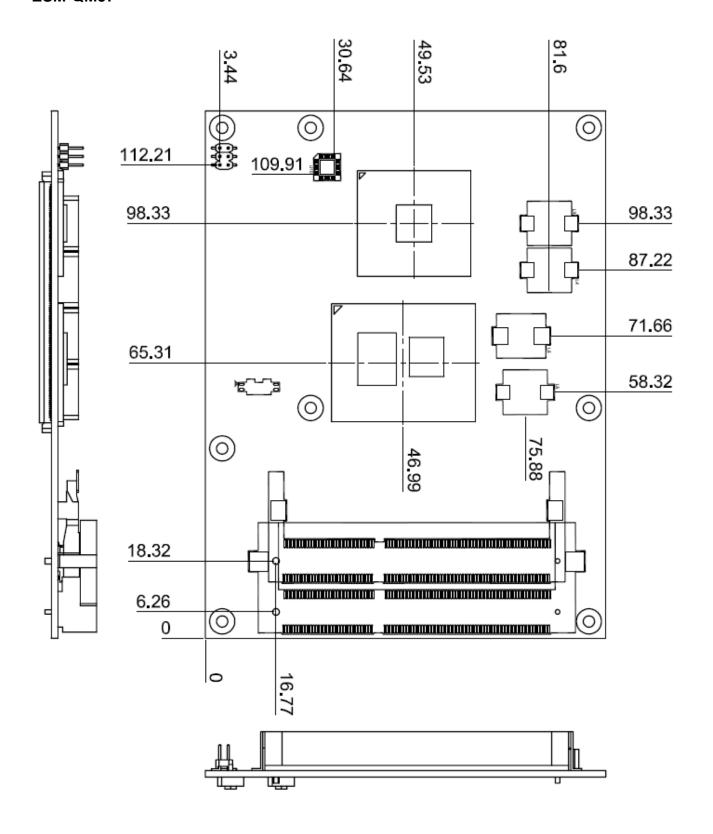

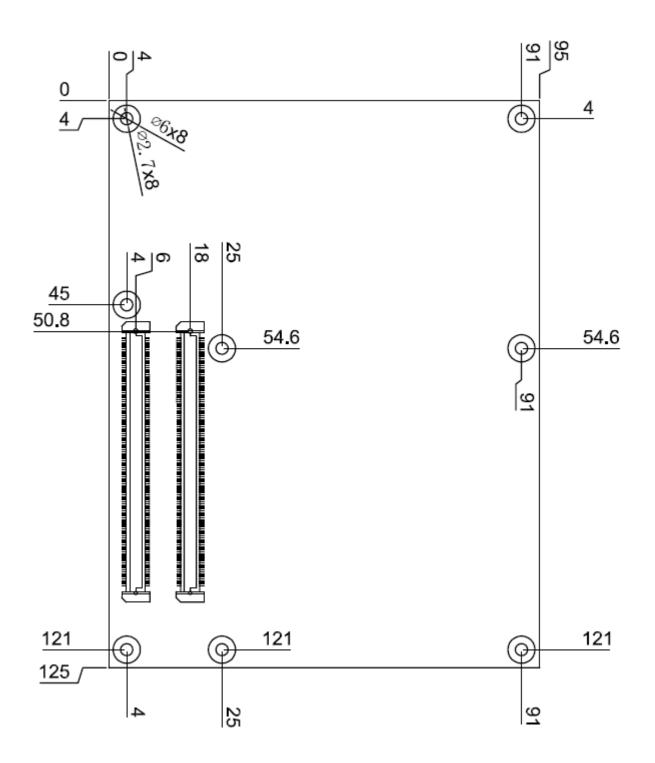

| Mochanical Drawing                                     | 91 |

# 1. Getting Started

## 1.1 Safety Precautions

#### Warning!

Always completely disconnect the power cord from your chassis whenever you work with the hardware. Do not make connections while the power is on. Sensitive electronic components can be damaged by sudden power surges. Only experienced electronics personnel should open the PC chassis.

#### Caution!

Always ground yourself to remove any static charge before touching the CPU card. Modern electronic devices are very sensitive to static electric charges. As a safety precaution, use a grounding wrist strap at all times. Place all electronic components in a static-dissipative surface or static-shielded bag when they are not in the chassis.

#### 1.2 Packing List

Before you begin installing your single board, please make sure that the following materials have been shipped:

- 1 x ESM-QM57 Intel Core i7/ Celeron COM Express Module

- 1 x Quick Installation Guide

- 1 x DVD-ROM contains the followings:

- User's Manual (this manual in PDF file)

- Chipset and Ethernet driver

If any of the above items is damaged or missing, contact your retailer.

## 1.3 Document Amendment History

| Revision        | Date       | Comment         |  |

|-----------------|------------|-----------------|--|

| 1 <sup>st</sup> | April 2011 | Initial Release |  |

## 1.4 Manual Objectives

This manual describes in detail the Avalue Technology ESM-QM57 Single Board.

We have tried to include as much information as possible but we have not duplicated information that is provided in the standard IBM Technical References, unless it proved to be necessary to aid in the understanding of this board.

We strongly recommend that you study this manual carefully before attempting to interface with ESM-QM57 series or change the standard configurations. Whilst all the necessary information is available in this manual we would recommend that unless you are confident, you contact your supplier for guidance.

Please be aware that it is possible to create configurations within the CMOS RAM that make booting impossible. If this should happen, clear the CMOS settings, (see the description of the Jumper Settings for details).

If you have any suggestions or find any errors concerning this manual and want to inform us of these, please contact our Customer Service department with the relevant details.

## 1.5 System Specifications

| System                     |                                                                                                   |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| СРИ                        | Intel Core i7 620LE (2.00GHz) / 620 UE (1.06GHz)                                                  |  |  |  |

| BIOS                       | AMI 8 MBit Flash BIOS                                                                             |  |  |  |

| System Chipset             | Intel QM57                                                                                        |  |  |  |

| I/O Chip                   | N/A                                                                                               |  |  |  |

| System Memory              | Two 204-pin SODIMM sockets up to 8GB DDR3 800/1066 SDRAM                                          |  |  |  |

| Expansion                  | LPC, 4 PCI (PCI Rev. 2.3 compliant), 6 PCIe x1, 1 PCIe x16 (shared with SDVO, HDMI & Displayport) |  |  |  |

| TPM                        | Nuvoton WPCT200A                                                                                  |  |  |  |

| I/O                        |                                                                                                   |  |  |  |

| MIO                        | 1 x EIDE (Ultra DMA 100), LPC, SMbus/I <sup>2</sup> C Bus, 4 x SATA                               |  |  |  |

| USB                        | 8 x USB 2.0 ports                                                                                 |  |  |  |

| DIO                        | 4-bit GPI and 4-bit GPO                                                                           |  |  |  |

| Display                    |                                                                                                   |  |  |  |

| Chipset                    | Intel QM57                                                                                        |  |  |  |

| Resolution                 | CRT mode: 2048 x 1536 @ 60 Hz                                                                     |  |  |  |

| Nesolution                 | LCD/Simultaneous mode: 1600x1200 @ 75Hz                                                           |  |  |  |

| Multiple                   | CRT + LVDS, CRT+ SDVO, LVDS + SDVO                                                                |  |  |  |

| Display                    | CKT FEVES, CKT GEVO, EVES TOEVO                                                                   |  |  |  |

| LCD<br>Interface           | Dual-Channel 18/24-bit LVDS                                                                       |  |  |  |

| TV-out                     | N/A                                                                                               |  |  |  |

| HDMI                       | HDML DisplayPort chared with PCloy16                                                              |  |  |  |

| DisplayPort                | HDMI, DisplayPort shared with PClex16                                                             |  |  |  |

| Audio                      |                                                                                                   |  |  |  |

| Chipset                    | Intel QM57                                                                                        |  |  |  |

| Audio Interface            | Intel High Definition Audio                                                                       |  |  |  |

| Ethernet                   |                                                                                                   |  |  |  |

| LAN Chip                   | Intel 82577LM (PHY) Gigabit LAN , supports Wake on LAN                                            |  |  |  |

| Ethernet Interface         | 1000Base-Tx Gigabit Ethernet compatible                                                           |  |  |  |

| Mechanical & Environmental |                                                                                                   |  |  |  |

| Power Requirement          | +9 ~ +19V                                                                                         |  |  |  |

| ACPI                       | Single power ATX Support S0, S3, S4, S5 ACPI 3.0 Compliant                                        |  |  |  |

| Power Type                 | AT / ATX                                                                                          |  |  |  |

#### **User's Manual**

| Operating Temp.    | 0~60°C                                   |  |  |

|--------------------|------------------------------------------|--|--|

| Storage Temp.      | -40 ~ 75°C                               |  |  |

| Operating Humidity | 0%~90% relative humidity, non-condensing |  |  |

| Size (L x W)       | 5" x 3.7" (125 mm x 95 mm)               |  |  |

| Weight             | 0.44 lbs (0.2 Kg)                        |  |  |

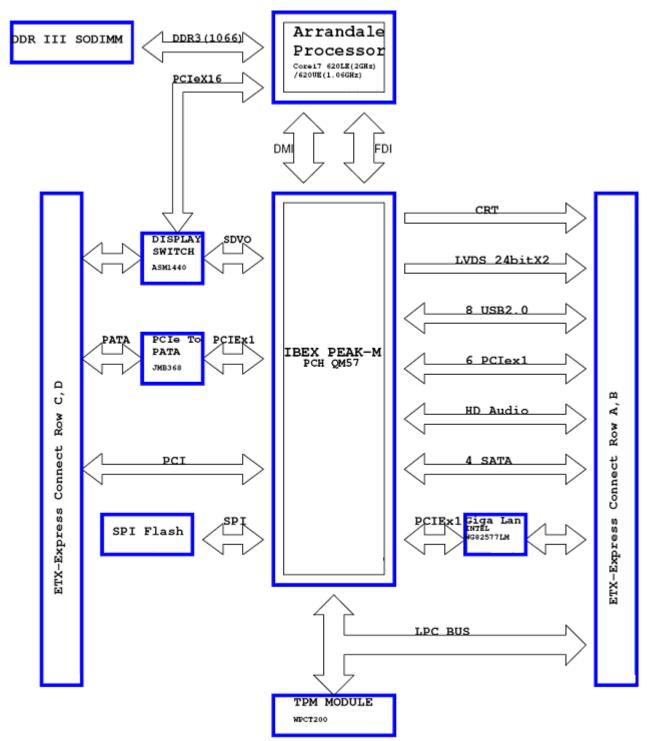

## 1.6 Architecture Overview – Block Diagram

The following block diagram shows the architecture and main components of ESM-QM57

# 2. Hardware Configuration

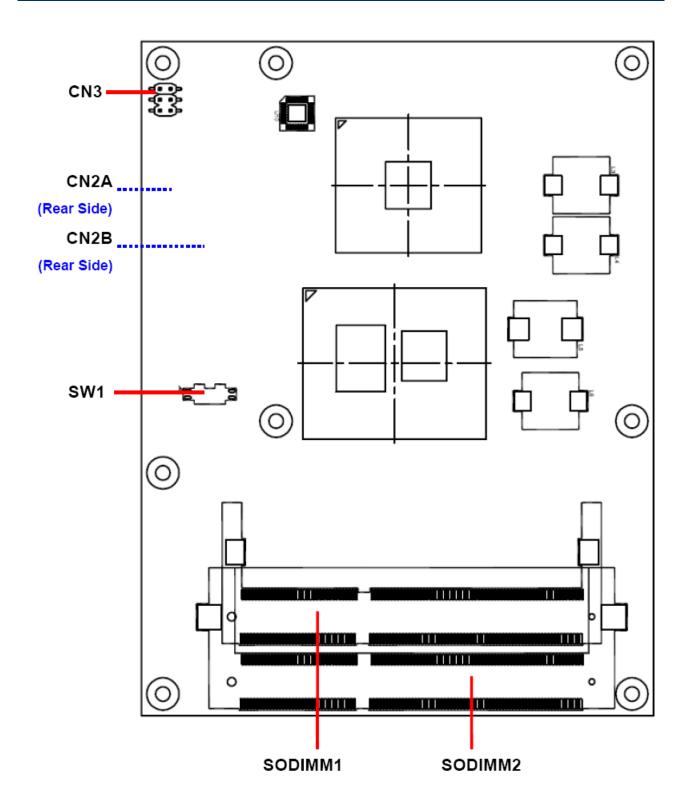

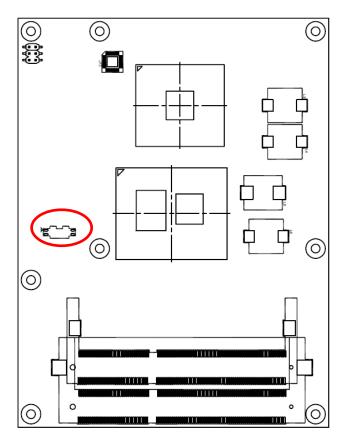

## 2.1 Product Overview

## 2.2 Installation Procedure

This chapter gives you the instructions on how to setup your system.

- 1. Turn off the power supply.

- 2. Insert the SODIMM module (be careful with the orientation).

- 3. Insert all external cables for hard disk, floppy, keyboard, mouse, USB etc. except for flat panel. A CRT monitor must be connected in order to change CMOS settings to support flat panel.

- 4. Connect power supply to the board via the ATXPWR.

- 5. Turn on the power.

- 6. Enter the BIOS setup by pressing the delete key during boot up. (more details on page 37)

- 7. If TFT panel display is to be utilized, make sure the panel voltage is correctly set before connecting the display cable and turning on the power.

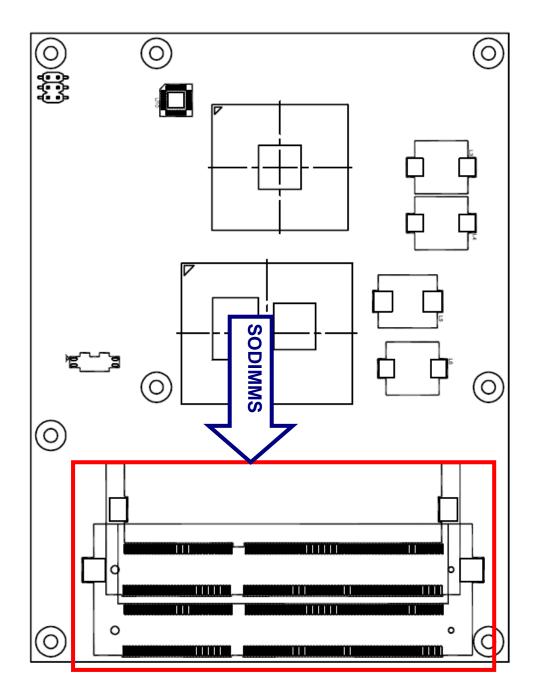

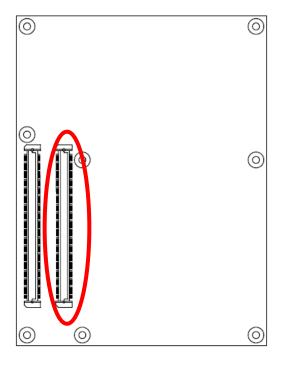

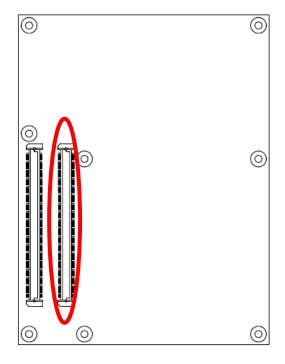

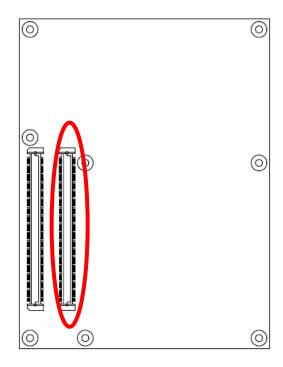

## 2.2.1 Main Memory

ESM-QM57 provides two 204-pin SODIMM sockets up to 8GB DDR3 800/1066 SDRAM

Make sure to unplug the power supply before adding or removing SODIMMs or other system components. Failure to do so may cause severe damage to both board and components.

- Locate the SODIMM socket on the board.

- Hold two edges of the SODIMM module carefully. Keep away from touching its connectors.

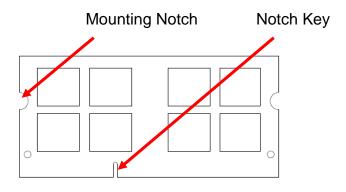

- Align the notch key on the module with the rib on the slot.

- Firmly press the module into the socket which automatically snaps into the mounting notch. Do not force the SODIMM module in with extra force as the SODIMM module only fits in one direction.

204-pin DDR3 SODIMM

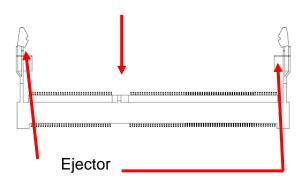

To remove the SODIMM modules, push the two ejector tabs on the slot outward simultaneously, and then pull out the SODIMM module.

#### Note:

- (1) Please do not change any DDR3 SDRAM parameter in BIOS setup to increase your system's performance without acquiring technical information in advance.

- (2) Static electricity can damage the electronic components of the computer or optional boards. Before starting these procedures, ensure that you are discharged of static electricity by touching a grounded metal object briefly.

#### 2.3 Connector List

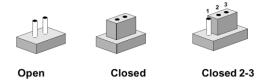

You can configure your board to match the needs of your application by setting jumpers. A jumper is the simplest kind of electric switch.

It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" a jumper you connect the pins with the clip. To "open" a jumper you remove the clip. Sometimes a jumper will have three pins, labeled 1, 2, and 3. In this case, you would connect either two pins.

The jumper settings are schematically depicted in this manual as follows:

A pair of needle-nose pliers may be helpful when working with jumpers.

Connectors on the board are linked to external devices such as hard disk drives, a keyboard, or floppy drives. In addition, the board has a number of jumpers that allow you to configure your system to suit your application.

If you have any doubts about the best hardware configuration for your application, contact your local distributor or sales representative before you make any changes.

The following tables list the function of each of the board's jumpers and connectors.

| Connectors |                                 |                           |

|------------|---------------------------------|---------------------------|

| Label      | Function                        | Note                      |

| CN3        | (Reserved for BIOS programming) | 3 x 2 header, pitch 2.0mm |

| CN2A       | COM Express connector 1         |                           |

| CN2B       | COM Express connector 2         |                           |

| SODIMM1    | 204-pin DDR3 SDRAM DIMM socket  |                           |

| SODIMM2    | 204-pin DDR3 SDRAM DIMM socket  |                           |

| SW1        | AT/ATX mode selector            |                           |

## 2.4 Setting Jumpers & Connectors

#### AT/ATX mode selector (SW1) 2.4.1

AT/ATX mode AT mode OFF ON ATX mode\* OFF ON

## 2.4.1.1 Signal Description –AT/ATX mode selection

| AT/ATX mode | Description                                    |

|-------------|------------------------------------------------|

| AT mode     | This Mode supports AT power supply, no need    |

| 1<br>2      | to press Power button to enable power on/off   |

| ATX mode    | This Mode supports ATX power supply. Press the |

| 1<br>2      | ATX power button to enable power on/off        |

<sup>\*</sup>Default

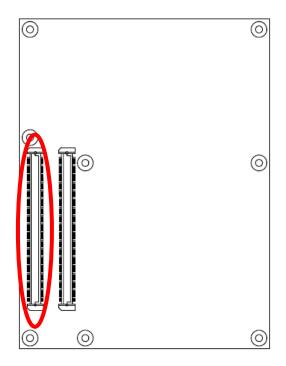

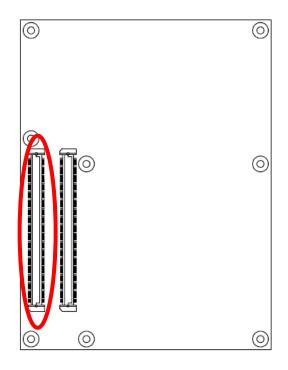

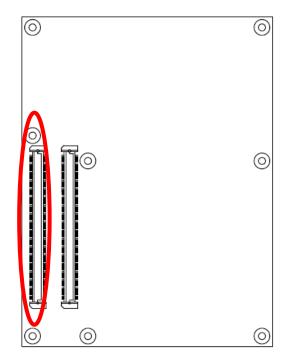

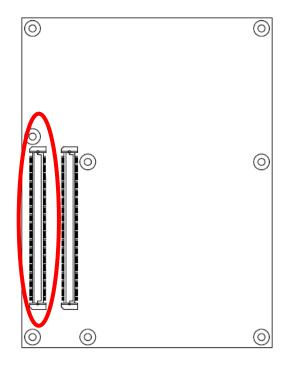

## 2.4.2 COM Express Connector 1 (CN2A)

(Rear side)

| Signal         | PIN | PIN | Signal       |

|----------------|-----|-----|--------------|

| GND            | A1  | B1  | GND          |

| PCIE_MDI3-     | A2  | B2  | PCIE_ACT#    |

| PCIE_MDI3+     | А3  | ВЗ  | LPC_FRAME#   |

| PCIE_LINK100#  | A4  | В4  | LPC_AD0      |

| PCIE_LINK1000# | A5  | B5  | LPC_AD1      |

| PCIE_MDI2-     | A6  | В6  | LPC_AD2      |

| PCIE_MDI2+     | A7  | В7  | LPC_AD3      |

| PCIE_LINK#     | A8  | B8  | LPC_DRQ0#    |

| PCIE_MDI1-     | A9  | В9  | LPC_DRQ1#    |

| PCIE_MDI1+     | A10 | B10 | CLK_LPC_33M  |

| GND            | A11 | B11 | GND          |

| PCIE_MDI0-     | A12 | B12 | PWRBTN#      |

| PCIE_MDI0+     | A13 | B13 | SMB_CLK      |

| LAN_1.9V       | A14 | B14 | SMB_DATA     |

| SLP_S3#        | A15 | B15 | LINKALERT#   |

| SATAP0_TXP     | A16 | B16 | SATAP1_TXP   |

| SATAP0_TXN     | A17 | B17 | SATAP1_TXN   |

| SLP_S4#        | A18 | B18 | PM_SUS_SATA# |

| SATAP0_RXP     | A19 | B19 | SATAP1_RXP   |

| SATAP0_RXN     | A20 | B20 | SATAP1_RXN   |

| GND            | A21 | B21 | GND          |

| SATAP2_TXP     | A22 | B22 | SATAP3_TXP   |

| SATAP2_TXN     | A23 | B23 | SATAP3_TXN   |

| SLP_S5#        | A24 | B24 | POWER_OK     |

| SATAP2_RXP     | A25 | B25 | SATAP3_PXP   |

| SATAP2_RXN     | A26 | B26 | SATAP3_PXN   |

| PM_BATLOW#     | A27 | B27 | WDT          |

| SATA_LED#      | A28 | B28 | HAD_SDIN2    |

| HAD_SYNC       | A29 | B29 | HAD_SDIN1    |

| HAD_RST#       | A30 | B30 | HAD_SDIN0    |

#### **User's Manual**

(Rear side)

| Signal        | PIN | PIN | Signal      |

|---------------|-----|-----|-------------|

| GND           | A31 | B31 | GND         |

| HAD_BIT_CLK   | A32 | B32 | HAD_SPKR    |

| HAD_SDOUT     | A33 | B33 | I2C_CLK     |

| BIOS_DISABLE# | A34 | B34 | I2C_DAT     |

| PM_THRMTRIP#  | A35 | B35 | ETX_THRM#   |

| USB_PN6       | A36 | B36 | USB_PN7     |

| USB_PP6       | A37 | B37 | USB_PP7     |

| USB_OC67#     | A38 | B38 | USB_OC45#   |

| USB_PN4       | A39 | B39 | USB_PN5     |

| USB_PP4       | A40 | B40 | USB_PP5     |

| GND           | A41 | B41 | GND         |

| USB_PN2       | A42 | B42 | USB_PN3     |

| USB_PP2       | A43 | B43 | USB_PP3     |

| USB_OC23#     | A44 | B44 | USB_OC01#   |

| USB_PN0       | A45 | B45 | USB_PN1     |

| USB_PP0       | A46 | B46 | USB_PP1     |

| RTC_VCC       | A47 | B47 | PLTRST#     |

| PLTRST#       | A48 | B48 | EXCD1_CPPE# |

| EXCD0_CPPE#   | A49 | B49 | PM_SYSRST#  |

| PCI_SERIRQ    | A50 | B50 | BU_PLTRST#  |

| GND           | A51 | B51 | GND         |

| PCIE8_TX+     | A52 | B52 | PCIE8_RX+   |

| PCIE8_TX-     | A53 | B53 | PCIE8_RX-   |

| ETX_GPIO43    | A54 | B54 | ETX_GPIO10  |

| PCIE7_TX+     | A55 | B55 | PCIE7_RX+   |

| PCIE7_TX-     | A56 | B56 | PCIE7_RX-   |

| GND           | A57 | B57 | ETX_GPIO2   |

| PCIE4_TX+     | A58 | B58 | PCIE4_RX+   |

| PCIE4_TX-     | A59 | B59 | PCIE4_RX-   |

| GND           | A60 | B60 | GND         |

(Rear side)

| Signal        | PIN | PIN | Signal         |

|---------------|-----|-----|----------------|

| PCIE3_TX+     | A61 | B61 | PCIE3_RX+      |

| PCIE3_TX-     | A62 | B62 | PCIE3_RX-      |

| ETX_GPIO45    | A63 | B63 | ETX_GPIO15     |

| PCIE2_TX+     | A64 | B64 | PCIE2_RX+      |

| PCIE2_TX-     | A65 | B65 | PCIE2_RX-      |

| GND           | A66 | B66 | PCIE_WAKE#     |

| ETX_GPIO46    | A67 | B67 | PM_RI#         |

| PCIE1_TX+     | A68 | B68 | PCIE1_RX+      |

| PCIE1_TX-     | A69 | B69 | PCIE1_RX-      |

| GND           | A70 | B70 | GND            |

| LVDSA_DATA0   | A71 | B71 | LVDSB_DATA0    |

| LVDSA_DATA#0  | A72 | B72 | LVDSB_DATA#0   |

| LVDSA_DATA1   | A73 | B73 | LVDSB_DATA1    |

| LVDSA_DATA#1  | A74 | B74 | LVDSB_DATA#1   |

| LVDSA_DATA2   | A75 | B75 | LVDSB_DATA2    |

| LVDSA_DATA#2  | A76 | B76 | LVDSB_DATA#2   |

| LVDS_VDD_EN   | A77 | B77 | LVDSB_DATA3    |

| LVDSA_DATA3   | A78 | B78 | LVDSB_DATA#3   |

| LVDSA_DATA#3  | A79 | B79 | LVDS_BKLT_EN   |

| GND           | A80 | B80 | GND            |

| LVDSA_CLK     | A81 | B81 | LVDSB_CLK      |

| LVDSA_CLK#    | A82 | B82 | LVDSB_CLK#     |

| LVDS_DDC_CLK  | A83 | B83 | LVDS_BKLT_CTRL |

| LVDS_DDC_DATA | A84 | B84 | 5VSB           |

| ETX_GPIO7     | A85 | B85 | 5VSB           |

| KBRST#        | A86 | B86 | 5VSB           |

| H_A20GATE     | A87 | B87 | 5VSB           |

| CLK_PCIE_ETX+ | A88 | B88 | NC             |

| CLK_PCIE_ETX- | A89 | B89 | CRT_RED        |

| GND           | A90 | B90 | GND            |

#### **User's Manual**

(Rear side)

| Signal     | PIN  | PIN  | Signal       |

|------------|------|------|--------------|

| CLK_PEG_A+ | A91  | B91  | CRT_GREEN    |

| CLK_PEG_A- | A92  | B92  | CRT_BLUE     |

| ETX_GPIO09 | A93  | B93  | CRT_HSYNC    |

| GPIO06     | A94  | B94  | CRT_VSYNC    |

| GPIO07     | A95  | B95  | CRT_DDC_CLK  |

| GND        | A96  | B96  | CRT_DDC_DATA |

| +12V       | A97  | B97  | NC           |

| +12V       | A98  | B98  | NC           |

| +12V       | A99  | B99  | NC           |

| GND        | A100 | B100 | GND          |

| +12V       | A101 | B101 | +12V         |

| +12V       | A102 | B102 | +12V         |

| +12V       | A103 | B103 | +12V         |

| +12V       | A104 | B104 | +12V         |

| +12V       | A105 | B105 | +12V         |

| +12V       | A106 | B106 | +12V         |

| +12V       | A107 | B107 | +12V         |

| +12V       | A108 | B108 | +12V         |

| +12V       | A109 | B109 | +12V         |

| GND        | A110 | B110 | GND          |

## 2.4.2 Signal Description – COM Express Connector 1 (CN2A)

## 2.4.2.1 Audio Signals

| Signal       | Signal Description                                              |

|--------------|-----------------------------------------------------------------|

| AC_SYNC      | 48kHz fixed-rate, sample-synchronization signal to the CODEC(s) |

| AC_RST#      | Reset output to AC97 CODEC, active low.                         |

| AC_SDIN[0:2] | Serial TDM data inputs from up to 3 CODECs.                     |

| AC_BITCLK    | 12.228 MHz serial data clock generated by the external CODEC(s) |

| AC_SDOUT     | Serial TDM data output to the CODEC.                            |

## 2.4.2.2 Gigabit Ethernet Signals

| Signal           |                                                                                                                                                                                                         | Signal De                | escription              |           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|-----------|

|                  | Gigabit Ethernet Controller 0: Media Dependent Interface Differential Pairs 0,1,2,3.  The MDI can operate in 1000, 100 and 10 Mbit / sec modes. Some pairs are unused in some modes, per the following: |                          |                         |           |

| CDEO MDIO:21 ./  |                                                                                                                                                                                                         | 1000B-T                  | 100B-T                  | 10B-T     |

| GBE0_MD[0:3] +/- | MDI[0]+/-                                                                                                                                                                                               | B1_DA+/                  | TX+/-                   | TX+/-     |

|                  | MDI[1]+/                                                                                                                                                                                                | B1_DB+/                  | RX+/-                   | RX+/-     |

|                  | MDI[2]+/                                                                                                                                                                                                | B1_DC+/                  | X                       | X         |

|                  | MDI[3]+/                                                                                                                                                                                                | B1_DD+/                  | X                       | X         |

| GBE0_ACT#        | Gigabit Ethernet Cor                                                                                                                                                                                    | troller 0 activity indic | cator, active low.      |           |

| GBE0_Link#       | Gigabit Ethernet Cor                                                                                                                                                                                    | troller 0 link indicato  | r, active low.          |           |

| GBE0_Link100#    | Gigabit Ethernet Cor                                                                                                                                                                                    | troller 0 100 Mbit / s   | ec link indicator, acti | ve low.   |

| GBE0_Lin1000#    | Gigabit Ethernet Cor                                                                                                                                                                                    | troller 0 1000 Mbit /    | sec link indicator, ac  | tive low. |

## 2.4.2.3 GPIO Signals

| Signal   | Signal Description                                                             |

|----------|--------------------------------------------------------------------------------|

| GPI[0:3] | General purpose input pins. Pulled high internally on the module.              |

| GPO[0:3] | General purpose output pins. Upon a hardware reset, these outputs will be low. |

## 2.4.2.4 Flat Panel LVDS Signals

| Signal                                     | Signal Description                                                                                                                                                                                                           |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIASON                                     | Controls panel contrast voltage.                                                                                                                                                                                             |

| DIGON                                      | Controls panel digital power.                                                                                                                                                                                                |

| ENBKL#                                     | Controls backlight power enable.                                                                                                                                                                                             |

| I <sup>2</sup> C_DAT, I <sup>2</sup> C_CLK | I <sup>2</sup> C interface for panel parameter EEPROM. This EERPOM is mounted on the LVDS receiver. The data in the EEPROM allows the EXT module to automatically set the proper timing parameters for a specific LCD panel. |

## 2.4.2.5 LPC Signals

| Signal        | Signal Description                            |

|---------------|-----------------------------------------------|

| LPC_FRAME#    | LPC frame indicates the start of an LPC cycle |

| LPC_AD[0:3]   | LPC multiplexed address, command and data bus |

| LPC_DRQ[0:1]# | LPC serial DMA request                        |

| LPC_CLK       | LPC clock output - 33MHz nominal              |

| LPC_SERIRQ    | LPC serial interrupt                          |

## 2.4.2.6 Miscellaneous Signals

| Signal               | Signal Description                                                                   |

|----------------------|--------------------------------------------------------------------------------------|

| I <sup>2</sup> C_CK  | General purpose I <sup>2</sup> C port clock output                                   |

| I <sup>2</sup> C_DAT | General purpose I <sup>2</sup> C port data I/O line                                  |

| SPKR                 | Output for audio enunciator - the "speaker" in PC-AT systems                         |

| BIOS_DISABLE#        | Module BIOS disable input. Pull low to disable module BIOS. Used to allow            |

|                      | off-module BIOS implementations.                                                     |

| KB_RST#              | Input to module from (optional) external keyboard controller that can force a reset. |

|                      | Pulled high on the module. This is a legacy artifact of the PC-AT.                   |

| KB_A20GATE           | Input to module from (optional) external keyboard controller that can be used to     |

|                      | control the CPU A20 gate line. The A20GATE restricts the memory access to the        |

|                      | bottom megabyte and is a legacy artifact of the PC-AT. Pulled low on the module.     |

## 2.4.2.7 PCI Express Signals

| Signal           | Signal Description                                                                       |

|------------------|------------------------------------------------------------------------------------------|

| PCIE_TX[0:4] +/- | PCI Express Differential Transmit Pair 0-4                                               |

| PCIE_RX[0:4] +/- | PCI Express Differential Receive Pair 0-4                                                |

| PCIE0_CK_REF+/-  | Reference clock output for PCI Express lanes 0-7 and for PCI Express Graphics lanes 0-15 |

## 2.4.2.8 Power Signals

| Signal     | Signal Description                                                                  |

|------------|-------------------------------------------------------------------------------------|

| VCC_5V_SBY | Standby power input: +5.0V nominal. See Electrical Specifications for allowable     |

|            | input range. If VCC5_SBY is used, all available VCC_5V_SBY pins on the              |

|            | connector(s) must be used. Only used for standby and suspend functions. May be      |

|            | left unconnected if these functions are not used in the system design.              |

| VCC_RTC    | Real-time clock circuit-power input. Nominally +3.0V. See Electrical Specifications |

|            | section for details.                                                                |

## 2.4.2.9 Power & System Management Signals

| Signal     | Signal Description                                                                |

|------------|-----------------------------------------------------------------------------------|

| SUS_S3#    | Indicates system is in Suspend to RAM state. Active low output.                   |

| SUS_S4#    | Indicates system is in Suspend to Disk state. Active low output.                  |

| SUS_S5#    | Indicates system is in Soft Off state. Also known as "PS_ON" and can be used to   |

| 000_00#    | control an ATX power supply.                                                      |

| BATLOW#    | Indicates that external battery is low                                            |

| PWRBTN#    | Power button to bring system out of S5 (soft off), active on rising edge.         |

| SMB CK     | System Management Bus bidirectional clock line. Power sourced through 5V          |

| SMB_CK     | standby rail and main power rails.                                                |

| SMB_DTA    | System Management Bus bidirectional data line. Power sourced through 5V           |

| SIVID_DTA  | standby rail and main power rails.                                                |

|            | System Management Bus Alert - input can be used to generate an SMI# (System       |

| SMB_ALERT# | Management Interrupt) or to wake the system. Power sourced through 5V standby     |

|            | rail and main power rails.                                                        |

| SUS_STAT#  | Indicates imminent suspend operation; used to notify LPC devices                  |

| PWR_OK     | Power OK from main power supply                                                   |

| THRMTRIP#  | Active low output indicating that the CPU has entered thermal shutdown.           |

| THRM#      | Input from off-module temp sensor indicating and over-temp situation.             |

| CVC DECET# | Reset button input. Active low input. System is held in hardware reset while this |

| SYS_RESET# | input is low, and comes out of reset upon release.                                |

| RSMRST#    | Resume reset input, active low. Resets power plane logic. May be left open on     |

|            | carrier board if not used.                                                        |

| WAKE0#     | PCI Express wake up signal                                                        |

| WAKE1#     | General purpose wake up signal                                                    |

## 2.4.2.10 SATA Signals

| Signal           | Signal Description                                        |

|------------------|-----------------------------------------------------------|

| SATA[0:3]_TX +/- | Serial ATA Channel 0-3 transmit differential pair.        |

| SATA[0:3]_RX +/- | Serial ATA Channel 0-3receive differential pair.          |

| ATA_ACT#         | ATA (parallel and serial) activity indicator, active low. |

## **2.4.2.11 VGA Signals**

| Signal                    | Signal Description                                                            |

|---------------------------|-------------------------------------------------------------------------------|

| VGA_RED                   | Red for monitor. Analog DAC output, designed to drive a 37.5-Ohm equivalent   |

|                           | load.                                                                         |

| VGA_GRN                   | Green for monitor. Analog DAC output, designed to drive a 37.5-Ohm equivalent |

|                           | load.                                                                         |

| VGA_BLU                   | Blue for monitor. Analog DAC output, designed to drive a 37.5-Ohm equivalent  |

|                           | load.                                                                         |

| VGA_HSYNC                 | Horizontal sync output to VGA monitor                                         |

| VGA_VSYNC                 | Vertical sync output to VGA monitor                                           |

| VGA_ I <sup>2</sup> C_CK  | DDC clock line (I2C port dedicated to identify VGA monitor capabilities)      |

| VGA_ I <sup>2</sup> C_DAT | DDC data line.                                                                |

## 2.4.2.12 USB Signals

| Signal       | Signal Description                           |

|--------------|----------------------------------------------|

| USB[0:7] +/- | USB differential pairs, channels 0 through 7 |

| USB_0_1_OC#  | USB over-current sense, USB channels 0 and 1 |

| USB_2_3_OC#  | USB over-current sense, USB channels 2 and 3 |

| USB_4_5_OC#  | USB over-current sense, USB channels 4 and 5 |

| USB_6_7_OC#  | USB over-current sense, USB channels 6 and 7 |

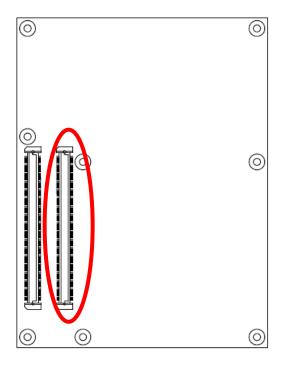

## 2.4.3 COM Express Connector 2 (CN2B)

(Rear side)

| Signal      | PIN | PIN | Signal      |

|-------------|-----|-----|-------------|

| GND         | C1  | D1  | GND         |

| IDE_PDD7    | C2  | D2  | IDE_PDD5    |

| IDE_PDD6    | СЗ  | D3  | IDE_PDD10   |

| IDE_PDD3    | C4  | D4  | IDE_PDD11   |

| IDE_PDD15   | C5  | D5  | IDE_PDD12   |

| IDE_PDD8    | C6  | D6  | IDE_PDD4    |

| IDE_PDD9    | C7  | D7  | IDE_PDD0    |

| IDE_PDD2    | C8  | D8  | IDE_PDDREQ  |

| IDE_PDD13   | C9  | D9  | IDE_PDIOW#  |

| IDE_PDD1    | C10 | D10 | IDE_PDDACK# |

| GND         | C11 | D11 | GND         |

| IDE_PDD14   | C12 | D12 | IDE_IRQ     |

| IDE_PDIORDY | C13 | D13 | IDE_PDA0    |

| IDE_PDIOR#  | C14 | D14 | IDE_PDA1    |

| PCI_PME#    | C15 | D15 | IDE_PDA2    |

| PCI_GNT#2   | C16 | D16 | IDE_PDCS1#  |

| PCI_REQ#2   | C17 | D17 | IDE_PDCS3#  |

| PCI_GNT#1   | C18 | D18 | BUF_PLTRST# |

| PCI_REQ#1   | C19 | D19 | PCI_GNT#3   |

| PCI_GNT#0   | C20 | D20 | PCI_REQ#3   |

| GND         | C21 | D21 | GND         |

| PCI_REQ#0   | C22 | D22 | PCI_AD1     |

| PCIRST#     | C23 | D23 | PCI_AD3     |

| PCI_AD0     | C24 | D24 | PCI_AD5     |

| PCI_AD2     | C25 | D25 | PCI_AD7     |

| PCI_AD4     | C26 | D26 | PCI_CBE#0   |

| PCI_AD6     | C27 | D27 | PCI_AD9     |

| PCI_AD8     | C28 | D28 | PCI_AD11    |

| PCI_AD10    | C29 | D29 | PCI_AD13    |

| PCI_AD12    | C30 | D30 | PCI_AD15    |

#### **User's Manual**

(Rear side)

| Signal      | PIN | PIN | Signal      |

|-------------|-----|-----|-------------|

| GND         | C31 | D31 | GND         |

| PCI_AD14    | C32 | D32 | PCI_PAR     |

| PCI_CBE#1   | C33 | D33 | PCI_SERR#   |

| PCI_PERR#   | C34 | D34 | PCI_STOP#   |

| PCI_LOCK#   | C35 | D35 | PCI_TRDY#   |

| PCI_DEVSEL# | C36 | D36 | PCI_FRAME#  |

| PCI_IRDY#   | C37 | D37 | PCI_AD16    |

| PCU_CBE#2   | C38 | D38 | PCI_AD18    |

| PCI_AD17    | C39 | D39 | PCI_AD20    |

| PCI_AD19    | C40 | D40 | PCI_AD22    |

| GND         | C41 | D41 | GND         |

| PCI_AD21    | C42 | D42 | PCI_AD24    |

| PCI_AD23    | C43 | D43 | PCI_AD26    |

| PCU_CBE#3   | C44 | D44 | PCI_AD28    |

| PCI_AD25    | C45 | D45 | PCI_AD30    |

| PCI_AD27    | C46 | D46 | INT_PIRQC#  |

| PCI_AD29    | C47 | D47 | INT_PIRQD#  |

| PCI_AD31    | C48 | D48 | PM_CLKRUN#  |

| INT_PIRQA#  | C49 | D49 | NC          |

| INT_PIRQB#  | C50 | D50 | CLK_PCI     |

| GND         | C51 | D51 | GND         |

| PEG_RX0     | C52 | D52 | PEG_TX0     |

| PEG_RX#0    | C53 | D53 | PEG_TX#0    |

| NC          | C54 | D54 | PEG_LAN_RV# |

| PEG_RX1     | C55 | D55 | PEG_TX1     |

| PEG_RX#1    | C56 | D56 | PEG_TX#1    |

| NC          | C57 | D57 | NC          |

| PEG_RX2     | C58 | D58 | PEG_TX2     |

| PEG_RX#2    | C59 | D59 | PEG_TX#2    |

| GND         | C60 | D60 | GND         |

(Rear side)

| Signal                   | PIN | PIN | Signal                  |

|--------------------------|-----|-----|-------------------------|

| PEG_RX3                  | C61 | D61 | PEG_TX3                 |

| PEG_RX#3                 | C62 | D62 | PEG_TX#3                |

| DDPB_AUX+                | C63 | D63 | DDPC_AUX+               |

| DDPB_AUX-                | C64 | D64 | DDPC_AUX-               |

| PEG_RX4                  | C65 | D65 | PEG_TX4                 |

| PEG_RX#4                 | C66 | D66 | PEG_TX#4                |

| HDMIC_CTRL_CLK           | C67 | D67 | GND                     |

| PEG_RX5                  | C68 | D68 | PEG_TX5                 |

| PEG_RX#5                 | C69 | D69 | PEG_TX#5                |

| GND                      | C70 | D70 | GND                     |

| PEG_RX6                  | C71 | D71 | PEG_TX6                 |

| PEG_RX#6                 | C72 | D72 | PEG_TX#6                |

| SDVO/<br>HDMIB_CTRL_DATA | C73 | D73 | SDVO/<br>HDMIB_CTRL_CLK |

| PEG_RX7                  | C74 | D74 | PEG_TX7                 |

| PEG_RX#7                 | C75 | D75 | PEG_TX#7                |

| GND                      | C76 | D76 | GND                     |

| HDMIC_CTRL_DATA          | C77 | D77 | PDIAG_S                 |

| PEG_RX8                  | C78 | D78 | PEG_TX8                 |

| PEG_RX#8                 | C79 | D79 | PEG_TX#8                |

| GND                      | C80 | D80 | GND                     |

| PEG_RX9                  | C81 | D81 | PEG_TX9                 |

| PEG_RX#9                 | C82 | D82 | PEG_TX#9                |

| HDMIB_HPD                | C83 | D83 | NC                      |

| GND                      | C84 | D84 | GND                     |

| PEG_RX10                 | C85 | D85 | PEG_TX10                |

| PEG_RX#10                | C86 | D86 | PEG_TX#10               |

| GND                      | C87 | D87 | GND                     |

| PEG_RX11                 | C88 | D88 | PEG_TX11                |

| PEG_RX#11                | C89 | D89 | PEG_TX#11               |

| GND                      | C90 | D90 | GND                     |

#### **User's Manual**

(Rear side)

| Cianal    | PIN  | PIN  | Cianal    |

|-----------|------|------|-----------|

| Signal    | PIN  | PIN  | Signal    |

| PEG_RX12  | C91  | D91  | PEG_TX12  |

| PEG_RX#12 | C92  | D92  | PEG_TX#12 |

| GND       | C93  | D93  | GND       |

| PEG_RX13  | C94  | D94  | PEG_TX13  |

| PEG_RX#13 | C95  | D95  | PEG_TX#13 |

| GND       | C96  | D96  | GND       |

| HDMIC_HPD | C97  | D97  | NC        |

| PEG_RX14  | C98  | D98  | PEG_TX14  |

| PEG_RX#14 | C99  | D99  | PEG_TX#14 |

| GND       | C100 | D100 | GND       |

| PEG_RX15  | C101 | D101 | PEG_TX15  |

| PEG_RX#15 | C102 | D102 | PEG_TX#15 |

| GND       | C103 | D103 | GND       |

| +12V      | C104 | D104 | +12V      |

| +12V      | C105 | D105 | +12V      |

| +12V      | C106 | D106 | +12V      |

| +12V      | C107 | D107 | +12V      |

| +12V      | C108 | D108 | +12V      |

| +12V      | C109 | D109 | +12V      |

| GND       | C110 | D110 | GND       |

## 2.4.3 Signal Description – COM Express Connector 2 (CN2B)

## 2.4.3.1 IDE Signals

| Signal      | Signal Description                                                                   |

|-------------|--------------------------------------------------------------------------------------|

| IDE_D[0:15] | Bidirectional data to / from IDE device.                                             |

| IDE_A[0:2]  | Address lines to IDE device.                                                         |

| IDE_REQ#    | IDE Device DMA Request. It is asserted by the IDE device to request a data transfer. |

| IDE_IOW#    | I/O writes line to IDE device. Data latched on trailing (rising) edge.               |

| IDE_ACK#    | IDE Device DMA Acknowledge.                                                          |

| IDE_IRQ     | Interrupt request from IDE device.                                                   |

| IDE_IORDY   | IDE device I/O ready input. Pulled low by the IDE device to extend the cycle.        |

| IDE_IOR#    | I/O read line to IDE device.                                                         |

| IDE_CS1#    | IDE Device Chip Select for 1F0h to 1FFh range.                                       |

| IDE_CS3#    | IDE Device Chip Select for 3F0h to 3FFhrange.                                        |

| IDE_RESET#  | Reset output to IDE device, active low.                                              |

## 2.4.3.2 HDMI Signals

| Signal               | Signal Description                                                              |

|----------------------|---------------------------------------------------------------------------------|

| SDVO/HDMIB_CTRL_DATA | SDVO or HDMI portB Control data                                                 |

| SDVO/HDMIB_CTRL_CLK  | SDVO or HDMI portB Control clock                                                |

| HDMIB_HPD            | Reserved for HDMI portB hot plug detection (add a resistor on R544 to activate) |

| HDMIC_CTRL_DATA      | Reserved for HDMI portC Control data (add a resistor on R180 to activate)       |

| HDMIC_CTRL_CLK       | Reserved for HDMI portC Control clock (add a resistor on R188 to activate)      |

| HDMIC_HPD            | Reserved for HDMI portC hot plug detection (add a resistor on R545 to activate) |

## 2.4.3.3 PCI Signals

| Signal        | Signal Description                                                                 |

|---------------|------------------------------------------------------------------------------------|

| PCI_AD[0:31]  | PCI bus multiplexed address and data lines                                         |

| DOL DME#      | PCI Power Management Event: PCI peripherals drive PME# to wake system from         |

| PCI_PME#      | low-power states S1–S5.                                                            |

| PCI_GNT[0:3]# | PCI bus master grant output lines, active low.                                     |

| PCI_REQ[0:3]# | PCI bus master request input lines, active low.                                    |

| PCI_RESET#    | PCI Reset output, active low.                                                      |

| PCI_CBE[0:3]  | PCI bus byte enable lines, active low                                              |

| DOL DEDD#     | Parity Error: An external PCI device drives PERR# when it receives data that has a |

| PCI_PERR#     | parity error.                                                                      |

| PCI_LOCK#     | PCI Lock control line, active low.                                                 |

| PCI_DEVSEL#   | PCI bus Device Select, active low.                                                 |

| PCI_IRD Y#    | PCI bus Initiator Ready control line, active low.                                  |

| PCI_IRQ[A:D]  | PCI interrupt request lines.                                                       |

| PCI_PAR       | PCI bus parity                                                                     |

| PCI_SERR#     | System Error: SERR# can be pulsed active by any PCI device that detects a          |

|               | system error condition.                                                            |

| PCI_STOP#     | PCI bus STOP control line, active low, driven by cycle initiator.                  |

| PCI_TRDY#     | PCI bus Target Ready control line, active low.                                     |

| PCI_FRAME#    | PCI bus Frame control line, active low.                                            |

| PCI_CLKRUN#   | Bidirectional pin used to support PCI clock run protocol for mobile systems.       |

| PCI_CLK       | PCI 33MHz clock output.                                                            |

## 2.4.3.4 PCI Express Graphics Signals

| Signal           | Signal Description                                                              |  |  |

|------------------|---------------------------------------------------------------------------------|--|--|

| DEC DVIO:151 ./  | PCI Express Graphics receive differential pairs. Some of these are multiplexed  |  |  |

| PEG_RX[0:15] +/- | with SDVO lines (see SDVO section).                                             |  |  |

| PEG_TX[0:15] +/- | PCI Express Graphics transmit differential pairs. Some of these are multiplexed |  |  |

|                  | with SDVO lines (see SDVO section).                                             |  |  |

| TYPE[0:2]        |                                                                                 |  |  |

| PEG_LANE_RV#     | PCI Express Graphics lane reversal input strap. Pull low to reverse lane order. |  |  |

|                  | Pulled high on module.                                                          |  |  |

| SDVO_DATA        | SDVO I <sup>2</sup> C data line - to set up SDVO peripherals.                   |  |  |

| SDVO_CLK         | SDVO I <sup>2</sup> C clock line - to set up SDVO peripherals.                  |  |  |

# 3. BIOS Setup

### 3.1 Introduction

The BIOS setup program allows users to modify the basic system configuration. In this following chapter will describe how to access the BIOS setup program and the configuration options that may be changed.

# 3.2 Starting Setup

The AMIBIOS™ is immediately activated when you first turn on the computer. The BIOS reads the system information contained in the CMOS and begins the process of checking out the system and configuring it. When it finishes, the BIOS will seek an operating system on one of the disks and then launch and turn control over to the operating system.

While the BIOS is in control, the Setup program can be activated in one of two ways:

By pressing <Del> immediately after switching the system on, or

By pressing the <Del> key when the following message appears briefly at the bottom of the screen during the POST (Power On Self Test).

#### Press DEL to enter SETUP

If the message disappears before you respond and you still wish to enter Setup, restart the system to try again by turning it OFF then ON or pressing the "RESET" button on the system case. You may also restart by simultaneously pressing <Ctrl>, <Alt>, and <Delete> keys. If you do not press the keys at the correct time and the system does not boot, an error message will be displayed and you will again be asked to.

Press F1 to Continue, DEL to enter SETUP

# 3.3 Using Setup

In general, you use the arrow keys to highlight items, press <Enter> to select, use the PageUp and PageDown keys to change entries, press <F1> for help and press <Esc> to quit. The following table provides more detail about how to navigate in the Setup program using the keyboard.

| Button               | Description                               |

|----------------------|-------------------------------------------|

| $\uparrow\downarrow$ | Select item                               |

| <b>←</b>             | Select screen                             |

| +/-                  | Change Option /Field                      |

| Enter                | Go to Sub Screen                          |

| PgUp key             | Previous page                             |

| PgDn key             | Next page                                 |

| Home                 | Go to top of screen                       |

| End                  | Go to bottom of Screen                    |

| F2, F3 key           | Change colors                             |

| F7 key               | Discard changes                           |

| F8 key               | Load Failsafe Defaults                    |

| F9 key               | Load Optimal Defauls                      |

| F10 key              | Save and Exit                             |

| Esc key              | Exit current page and return to Main Menu |

# Navigating Through The Menu Bar

Use the left and right arrow keys to choose the menu you want to be in.

**Note:** Some of the navigation keys differ from one screen to another.

### To Display a Sub Menu

Use the arrow keys to move the cursor to the sub menu you want. Then press <Enter>. A ">" pointer marks all sub menus.

## 3.4 Getting Help

Press F1 to pop up a small help window that describes the appropriate keys to use and the possible selections for the highlighted item. To exit the Help Window press <Esc> or the F1 key again.

## 3.5 In Case of Problems

If, after making and saving system changes with Setup, you discover that your computer no longer is able to boot, the AMIBIOS™ supports an override to the CMOS settings which resets your system to its defaults.

The best advice is to only alter settings which you thoroughly understand. To this end, we strongly recommend that you avoid making any changes to the chipset defaults. These defaults have been carefully chosen by both Award and your systems manufacturer to provide the absolute maximum performance and reliability. Even a seemingly small change to the chipset setup has the potential for causing you to use the override function.

## 3.6 BIOS setup

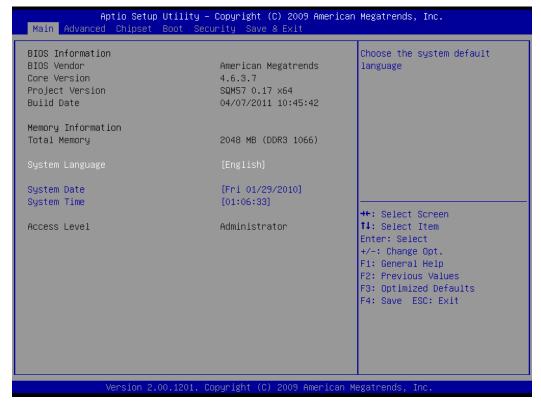

Once you enter the AMIBIOS™ CMOS Setup Utility, the Main Menu will appear on the screen. The Main Menu allows you to select from several setup functions and two exit choices. Use the arrow keys to select among the items and press <Enter> to accept and enter the sub-menu.

Note that a brief description of each highlighted selection appears at the bottom of the screen.

#### 3.6.1 Main Menu

This section allows you to record some basic hardware configurations on your computer and set the system clock.

## 3.6.1.1 System Language

This option allows choosing the system default language.

#### **3.6.1.2** System Date

Use the system time option to set the system time. Manually enter hours, minutes and seconds.

#### **3.6.1.3** System Time

Use the system Date option to set the system date. Manually enter the day, month and year.

40 ESM- QM57 User's Manual

Note: The BIOS setup screens shown in this chapter are for reference purposes only, and may not exactly match what you see on your screen. Visit the Avalue website (www.avalue.com.tw) to download the latest product and BIOS information.

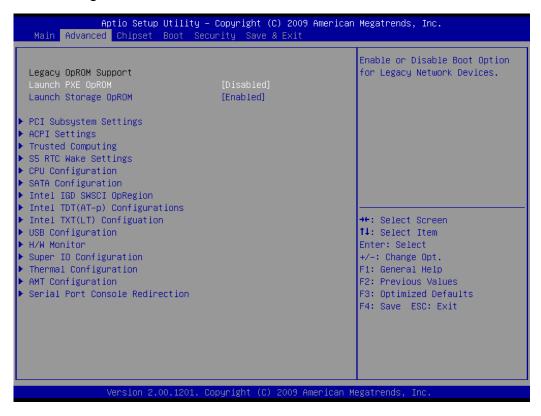

#### 3.6.2 Advanced Menu

This section allows you to configure your CPU and other system devices for basic operation through the following sub-menus.

| Item                 | Options   | Description                              |

|----------------------|-----------|------------------------------------------|

| Launch PXE OpROM     | Disabled, | Enable or disable Boot Option for Legacy |

| Launen PAE OPROM     | Enabled   | Network Devices                          |

| Launah Staraga OnBOM | Disabled, | Enable or disable Boot Option for Legacy |

| Launch Storage OpROM | Enabled   | Mass storage devices With Option ROM.    |

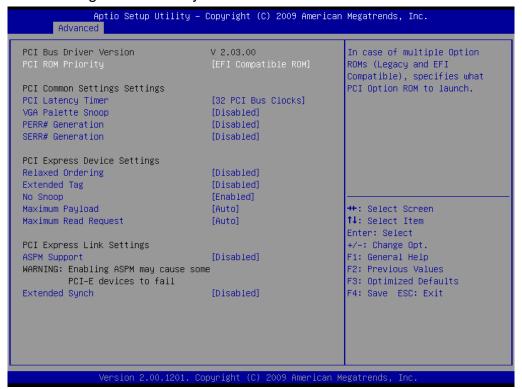

## 3.6.2.1 PCI Subsystem Settings

Use this item to configure PCI Subsystem

| Item               | Options                      | Description                            |

|--------------------|------------------------------|----------------------------------------|

| DCI DOM Drievity   | Legacy ROM                   | Specifies what PCI Option ROM to       |

| PCI ROM Priority   | EFI Compatible ROM [Default] | launch in case of multiple Option ROMs |

| DCI Latanav Timar  | 64/96/128/160/192/224/248    | Value to be programmed into PCI        |

| PCI Latency Timer  | 04/90/120/100/192/224/240    | Latency Timer Register.                |

| VCA Polotto Concer | Enabled                      | Enable or disable VGA Palette          |

| VGA Palette Snoop  | Disabled[Default]            | Snooping                               |

| PERR# Generation   | Enabled                      | Enable or disable PCI Device to        |

| PERR# Generation   | Disabled[Default]            | Generate PERR#                         |

| SERR# Generation   | Enabled                      | Enable or disable PCI Device to        |

| SERR# Generation   | Disabled[Default]            | Generate SERR#                         |

| Doloved Ordering   | Enabled                      | Enable or disable PCI Express Device   |

| Relaxed Ordering   | Disabled[Default]            | Relaxed ordering                       |

| Extended Tea       | Enabled                      | If enabled, would allow Device to use  |

| Extended Tag       | Disabled[Default]            | 8-bit Tag field as a requester         |

| No Choon           | Enabled[Default]             | Enable or disable PCI Express Device   |

| No Snoop           | Disabled                     | No Snoop option.                       |

### **User's Manual**

|                      | Auto[Default]              | Set Maximum Payload for PCI Express   |

|----------------------|----------------------------|---------------------------------------|

| Maximum Payload      | 128/256/512/1024/2048/4096 | Device or allow System BIOS to select |

|                      | Bytes                      | the value                             |

|                      | Auto[ <b>Default]</b>      | Set Maximum Read Request for PCI      |

| Maximum Read Request | 128/256/512/1024/2048/4096 | Express Device or allow System BIOS   |

|                      | Bytes                      | to select the value                   |

|                      | Disabled[ <b>Default</b> ] |                                       |

| ASPM Support         | Auto                       | Set ASPM level                        |

|                      | Force L0                   |                                       |

| Extended Synch       | Enabled                    | If Enabled, allows generation of      |

| Extended Synch       | Disabled[ <b>Default</b> ] | Extended Synchronization patterns     |

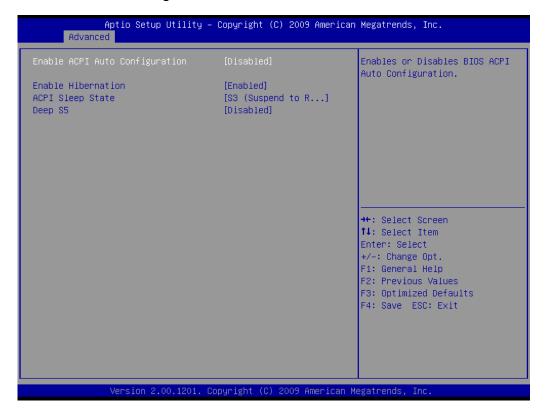

# 3.6.2.2 ACPI Settings

You can use this item to configure ACPI

| Item                           | Options                       | Description                           |

|--------------------------------|-------------------------------|---------------------------------------|

| Englis AODI Association        | Disabled [Default]            | Enables or Disables BIOS ACPI Auto    |

| Enable ACPI Auto Configuration | Enabled                       | Configuration.                        |

|                                |                               | Enables or Disables System ability to |

| Enable Hibernation             | Disabled,                     | Hibernate (OS/S4 Sleep State). This   |

| Enable Fibernation             | Enabled[Default]              | option may be not effective with some |

|                                |                               | OS.                                   |

|                                | Suspend Disable,              | Select the highest ACPI sleep state   |

| ACPI Sleep State               | S1 (CUP Stop Clock),          | the system will enter, when the       |

|                                | S3 (Suspend to RAM) [Default] | SUSPEND button is pressed.            |

| Doon S5                        | Disabled [Default]            | Enables or Disables does \$5 function |

| Deep S5                        | Enabled                       | Enables or Disables deep S5 function. |

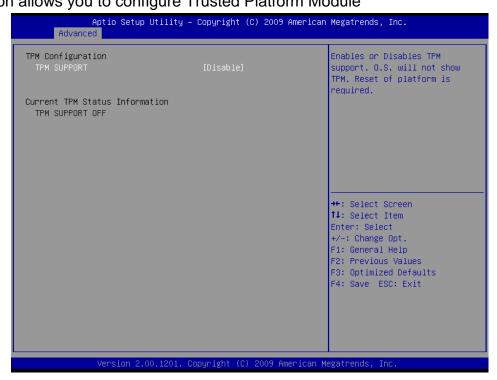

#### **Trusted computing** 3.6.2.3

This section allows you to configure Trusted Platform Module

| Item        | Options           | Description                      |  |

|-------------|-------------------|----------------------------------|--|

| TPM Support | Disabled[Default] | Enables or Disables TPM support  |  |

| тем эирроп  | Enabled           | Enables of Disables 1 FW Support |  |

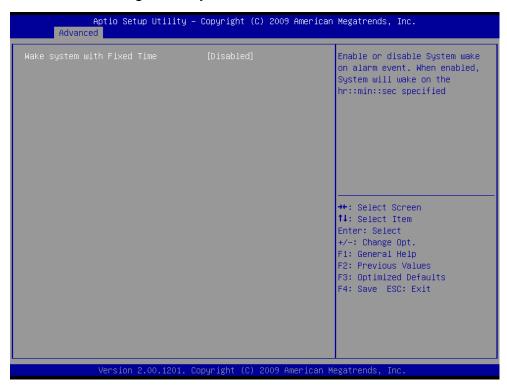

# 3.6.2.4 S5 RTC Wake Settings

Use the S5 RTC wake setting to set system wake in fixed time.

| Item                        | Options                           | Description                                                                                            |

|-----------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------|

| Wake system with fixed time | Disabled[ <b>Default]</b> Enabled | Enables or Disables wake on alarm event.  When enabled, system will wake on the specified hr:min::sec. |

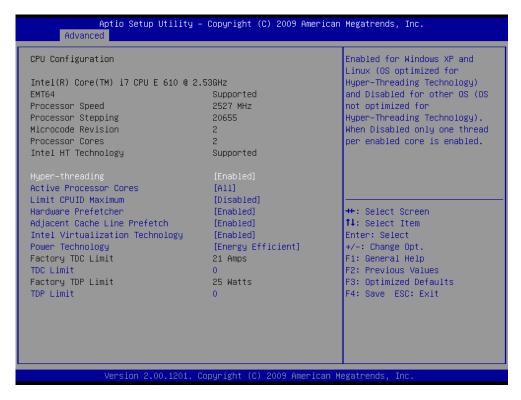

#### 3.6.2.5 **CPU Configuration**

Use the CPU configuration menu to view detailed CPU specification and configure the CPU.

| Item                            | Options                  | Description                                           |  |

|---------------------------------|--------------------------|-------------------------------------------------------|--|

|                                 |                          | Enabled for Windows XP and Linux (OS                  |  |

|                                 |                          | optimized for Hyper-Threading Technology)             |  |

| lluman Abna a din a             | Disabled,                | and Disabled for other OS (OS not optimized           |  |

| Hyper-threading                 | Enabled[Default]         | for Hyper-Threading Technology). When                 |  |

|                                 |                          | Disabled only one thread per enabled core is          |  |

|                                 |                          | enabled.                                              |  |

| Active Processor Cores          | All[Default]             | Number of cores to enable in each processor           |  |

| Active Processor Cores          | 1, 2                     | package.                                              |  |

| Limit CRUID Mavinous            | Disabled[Default]        | Disabled for Windows XP.                              |  |

| Limit CPUID Maximum             | Enabled                  |                                                       |  |

| Handware Brofesteleen           | Disabled,                | To trum on / off the NALC attraction or marketale are |  |

| Hardware Prefetcher             | Enabled[Default]         | To turn on/ off the MLC streamer prefetcher.          |  |

| Adiacout Cooks Line Burfatal    | Disabled,                | To turn on/ off prefetching of adjacent cache         |  |

| Adjacent Cache Line Prefetch    | Enabled[Default]         | lines.                                                |  |

|                                 | Dischlad                 | When enables, a VMM can utilize the                   |  |

| Intel Virtualization Technology | Disabled,                | additional hardware capabilities provided by          |  |

|                                 | Enabled[ <b>Default]</b> | Vanderpool Technology.                                |  |

|                  | Disabled,                  |                                       |

|------------------|----------------------------|---------------------------------------|

| Power Technology | Energy Efficient [Default] | Enable the power management features. |

|                  | Custom                     |                                       |

|                  |                            | Turbo-XE Mode Processor TDC Limit in  |

| TDC Limit        | 0                          | 1/8 A granularity. 0 means using the  |

|                  |                            | factory-configured value.             |

|                  |                            | Turbo-XE Mode Processor TDP Limit in  |

| TDP Limit        | 0                          | 1/8 W granularity. 0 means using the  |

|                  |                            | factory-configured value.             |

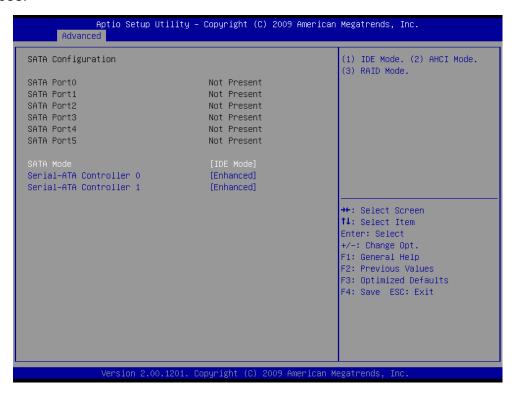

#### 3.6.2.6 **SATA Configuration**

It allows you to select the operation mode for SATA controller.

The choices:

| Item                    | Option             | Description                           |

|-------------------------|--------------------|---------------------------------------|

|                         | Disabled,          |                                       |

| SATA mode               | IDE mode,          | It allows you to select the operation |

| SATA IIIOGE             | AHCI mode,         | mode for SATA controller.             |

|                         | RAID mode          |                                       |

|                         | Disabled,          | Enabled/ Disabled Serial ATA          |

| Serial-ATA Controller 0 | Enhanced [Default] | Controller 0.                         |

|                         | Compatible         | Controller 0.                         |

| Serial-ATA Controller 1 | Disabled,          | Enabled/ Disabled Serial ATA          |

|                         | Enhanced[Default]  | Controller 0.                         |

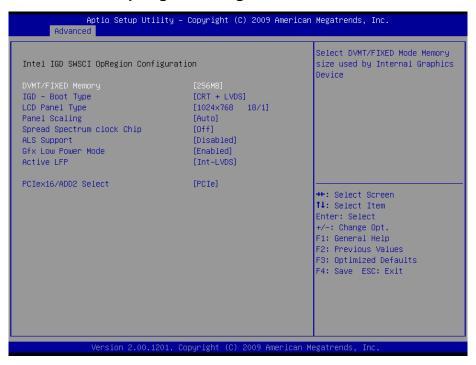

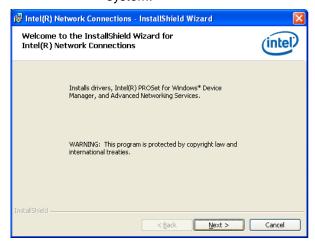

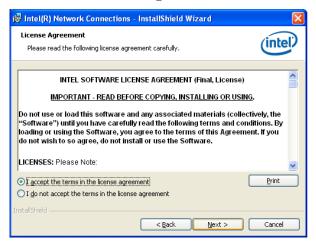

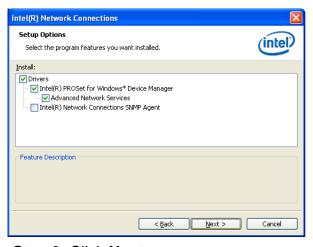

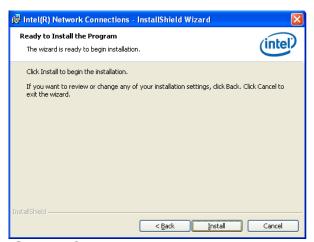

# 3.6.2.7 Intel IGD SWSCI OpRegion configuration